МИКРОКОНТРОЛЛЕРЫ СЕМЕЙСТВА MCS51

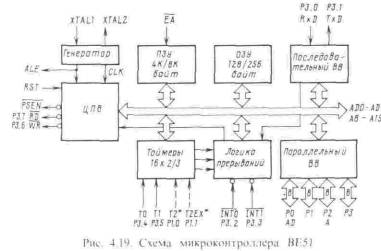

Введение в организацию ВЕ51. В состав однокристального МК ВЕ51 (рис. 4.19) входит 8-разрядный ЦП, управляющее ПЗУ, внутреннее ОЗУ данных, 32 линии прямого ВВ, четыре тестируе-мых входа, канал последовательного ВВ, два или три 16-разряд-ных таймера/счетчика Т и логика двухуровневой системы прерываний с пятью или шестью источниками запросов [64]. Эти средства образуют резидентную часть МК, размещенную непосредственно на кристалле. Базовая организация предоставляет встроенные средства расширения своих ресурсов, которые предусматривают либо реализацию вне кристалла всей памяти программ, либо расширение памяти, имеющейся внутри кристалла до 64К байт. Имеется возможность подключения дополнительной внешней па-мяти данных в 64К байт. Дальнейшее расширение ресурсов может быть выполнено только с помощью внешних средств.

Для сокращения ширины физического интерфейса большинство логических линий совмещаются. Так, при обращениях к внешней памяти порт РО выполняет роль совмещенной шины адреса/дан-ных, а Р2 шины старшей части адреса. Все выводы порта РЗ выполняют роль линий управления и специального ВВ.

В архитектуре ВЕ51 и ее модификациях использован стандартный для МК принцип независимости сред для хранения

программ и данных. Всего же архитектура ВЕ51 включает пять типов пространств, четыре из которых являются областями данных:

RSEG Пространство регистров

DSEG Пространство внутренней памяти данных

BSEG Битовое пространство данных

XSEG Пространство внешней памяти

CSEG Пространство программного кода

Однако пространство регистров, за исключением PC, и пространство битов, частично пересекаясь, физически совме-щаются с пространством DSEG, образуя единую внутреннюю среду для хранения данных, имеющую достаточно сложную структуру. Принцип наложения нескольких пространств данных друг на друга уже встречался в архитектуре ВЕ48. Это стандартный для однокристальных МС прием, позволяющий одни и те же физические данные рассматривать с разных позиций. В результате выбирается наиболее удобный для конкретного случая способ интерпретации тех или иных данных, в соответствии с которым и организуется доступ к ним.

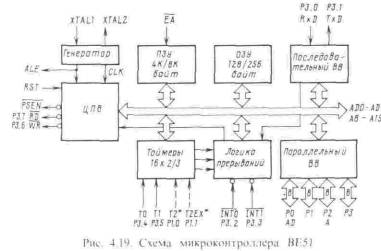

Набор регистров ВЕ51. Набор программно-доступных регист-ров процессора ВЕ51 приведен на рис. 4.20. Он является расширением набора регистров ВЕ48 , что обеспечивает совместимость архитектур ВЕ48 и ВЕ51 снизу вверх. Обе архитектуры относятся к классу аккумуляторных с переключае-мыми банками рабочих регистров. Поэтому центральным регистром набора считается 8-разрядный аккумулятор А, выполняющий обычные функции основного арифметического регистра.

Регистр В служит расширением аккумулятора А, необходимым для осуществления операций умножения и деления, причем он является как источником, так и приемником операндов. Во всех других операциях регистр В выполняет функции, определяемые пользователем.

Регистр слова состояния программы кроме флажков, входящих в PSW ВЕ48:

PSW.7 CY Перенос из старшего разряда АЛУ

PSW.6 АС Дополнительный перенос из младшей тетрады АЛУ

PSW.5 FO Флажок пользователя общего назначения

включает также флажки

PSW.2 OV Признак арифметического переполнения результата

PSW.1 Р Признак четности

Сюда же входит двухразрядное поле RS (Registers Select) выбора одного из четырех возможных банков рабочих регистров. Напом-ним, что в архитектуре ВЕ48 таких банков было всего два. Флажки признаков результата CY, АС и OV, как правило,

отражают состояние последней арифметической операции, флажок Р-четность содержимого А. Флажок переноса CY является аккумулятором булевого процессора. Функциональное назначение флажка FO определяется пользователем в конкретной ситуации.

Шестнадцатиразрядный программный счетчик PC управляет последовательностью выполнения команд, хранящихся в програм-мной памяти объемом до 64К байт. Указатель данных DPTR также имеет длину 16 разрядов, каждая его половина может быть адресована независимо от другой. Этот регистр используется в качестве адресного при пересылке констант из памяти программ и доступе к переменным из внешней памяти данных, а также для организации передачи управления.

Указатель стека образует системный стек глубиной до 256 байт. Он всегда содержит адрес последнего байта, занесенного в стек. Стек растет в сторону увеличения содержимого SP.

В МК BE 51 предусмотрено четыре банка по восемь рабочих регистров RO-R7 в каждом, переключаемых полем RS слова состояния программы. Регистры выполняют общецелевые функции промежуточного хранения данных. По аналогии с ВЕ48 два регистра RO и R1 каждого банка реализуют также функции 8-разрядных указателей данных.

Использование наборов рабочих регистров позволяет сущест-венно уменьшить длительность переключения контекстов ЦП, что очень важно для МС реального времени. Следует также отметить, что в ВЕ51 отсутствует ряд ограничений, накладываемых на обработку подпрограмм и процедур обслуживания прерываний, которые свойственны ВЕ48.

При сбросе МК все регистры устанавливаются в исходное состояние. Программный счетчик PC принимает значение ООООН, аккумулятор А-ООН; В-ООН, PSW-OOH, SP-07H и DPTR- ООООН. Сброс PC обеспечивает передачу управления по стартовому адресу ООООН, а установка SP в состояние 07Н поддерживает совместимость со стеком ВЕ48. Сброс PSW реализует выбор нулевого регистрового банка RBO, что также соответствует архитектуре ВЕ48.

Организация памяти ВЕ51. Пространство внутренней памяти DSEG имеет общий объем 256 байт. Однако организация ВЕ51 предусматривает реализацию только первой его половины (128 байт). В МК 8052 DSEG используется в полном объеме.

Подобно архитектуре ВЕ48 все банки рабочих регистров, а также системный стек в МК ВЕ51 располагаются во внутренней памяти данных и могут рассматриваться как обычные ячейки памяти. Существуют два способа адресации памяти данных МК:

прямой (direct) и косвенный (@Ri, i=0-l) через регистры RO, R1 выбранного в данный момент одного из банков RBO-RB3. При прямой адресации доступна только младшая половина адресного пространства внутренней памяти данных (128 байт), при косвенной обеспечивается доступ к любой ее ячейке (256 байт). Введение отсутствующей в ВЕ48 прямой адресации значительно расширило возможности обработки данных МК, в частности появились средства прямого доступа в соседние регистровые банки и стек системы, интерпретируемые как обычные ячейки памяти.

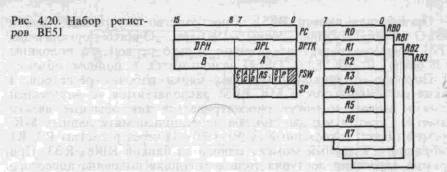

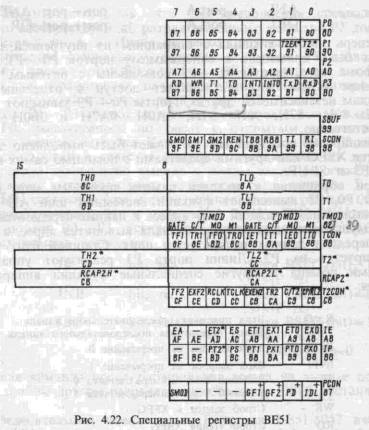

Микроконтроллер ВЕ51 имеет мощную и развитую подсистему ВВ и средства поддержки режима реального времени. Для их управления в МК предусмотрен ряд регистров, которые разме-щаются во второй половине прямо адресуемого пространства (рис. 4.21), образующей пространство специальных регистров (128 байт). Сюда же включены порты и основные регистры ЦП. Элементы, присутствующие только в модели 8052, отмечены знаком <*>, как и на рис. 4.22-4.24.

Центральный процессор ВЕ51 содержит специальную логику, предназначенную для выполнения нескольких однобитовых операций,- булев или одноразрядный процессор для вычисления буле-вых выражений. В основу булева процессора положен стандартный аккумуляторный принцип организации. В данном случае роль аккумулятора выполняет флажок переноса CY.

Для хранения булевых данных в архитектуре ВЕ51 предусмотрено специальное одноразрядное линейно упорядоченное пространство BSEG объемом 256 байт, которое физически совмещено с байтовым пространством данных DSEG. При этом одна часть пространства BSEG попадает на обычные ячейки памяти DSEG и может рассматриваться как область общего назначения. Обычно она используется для хранения булевых переменных. Другая часть пространства BSEG попадает на ячейки памяти, совмещенные с регистрами МК, что обеспечивает независимый доступ к их отдельным разрядам. В булевом пространстве определена только прямая адресация bit.

На рис. 4.21 в байтах пространства с прямой адресацией, которые размещены в булевом пространстве, указаны диапазоны адресов BSEG, относящихся к их разрядам. Например, старший разряд аккумулятора А, отождествленного с ячейкой пространства памяти с прямой адресацией под адресом ОЕОН, имеет адрес

пространства BSEG, равный ОЕ7Н. Двойная, а в ряде случаев тройная интерпретация отдельных данных дает возможность программисту выбирать тип доступа, наиболее подходящий для конкретного прикладного случая программирования. Все это позволяет повысить эффективность программного кода, его длину и скорость исполнения.

Пространство внешней памяти XSEG имеет объем 64К байт и реализуется внешними по отношению к МК средствами. Су-ществует единственная команда, поддерживающая связь с данным пространством

MOVX A,@Ri

;A<-XSEG(P2:Ri),

;i=0-l

MOVX A,@DPTR ;A<-XSEG(DPTR)

MOVX @Ri, A

;XSEG(P2:Ri)<-A,

;i=0-l

MOVX @DPTR, A ;XSEG(DPTR)<-A

В команде используются два типа адресации: косвенная регистро-вая по DPTR и страничная с номером страницы в Р2 и смещением в RO, R1. Это дает право рассматривать организацию внешней памяти ВЕ51 как линейную область или как область со страничной структурой.

Память программ CSEG адресуется 16-разрядным счетчиком PC и, следовательно, может иметь объем до 64К байт. Часть этой памяти (4К/8К байт с младшими адресами) может быть располо-жена на кристалле в виде программируемого маской ПЗУ или репрограммируемого электрически УСППЗУ. Она образует внут-реннюю память программ. Оставшаяся часть, реализуемая внеш-ними средствами вне кристалла, называется внешней памятью программ. С точки зрения программиста как внутренняя, так и внешняя память представляет собой единое пространство CSEG с равными правами доступа.

Среди особых точек пространства CSEG следует отметить

RESET OOOOH Стартовый адрес при сбросе системы

ЕХТI0 0003 Н Внешнее прерывание О

TIMERO ОООВН Прерывание таймера/счетчика О

EXTI1 0013Н Внешнее прерывание 1

TIMER1 001 ВН Прерывание таймера/счетчика 1

SINT 0023Н Прерывание последовательного порта

TIMER2 002ВН Прерывание таймера/счетчика 2 (только для 8052)

Пространство CSEG-однородное линейное пространство, в котором определены два основных способа передачи управления:

абсолютный addrl6 и относительный с помощью 8-разрядного смещения rel со знаком. Однако для некоторых команд оно представляет набор 2К-байтовых страниц:

ACALL addrll

;+(SP)<-PC, РСо-10<-addrll

AJMP addrll

;PCo-io<-addrll

Кроме того, предусмотрен переход по смещению относительно базы DPTR:

JMP @A+DPTR ;PC<-DPTR+A

Эти команды введены для поддержки совместимости с архитектурой ВЕ48. Специальная команда пересылки

MOVC A, @A+DPTR ;A<-CSEG(A+DPTR)

MOVC

A, @A+PC

;A<-CSEG(A+PC)

позволяет использовать содержимое программной памяти в качестве констант , доступных для чтения.

В МК ВЕ51 имеется возможность совмещения внешней части CSEG с пространством XSEG. Такое совмещение поможет распространить на область CSEG операции и способы доступа к XSEG, в частности станет осуществимой операция записи, что может быть использовано при загрузке программ из внешней памяти.

4.11. Периферийные средства ВЕ51

Порты ввода-вывода. Подсистема ВВ микроконтроллера ВЕ51 размещается непосредственно на кристалле. Для В В данных и управления процессом их передачи в состав МК введен ряд портов данных и регистров управления/состояния, совокупность которых образует набор специальных регистров (рис. 4.22).

Физическая система ВВ микроконтроллера ВЕ51 состоит из четырех двунаправленных 8-разрядных портов РО-РЗ. Все порты ВВ отображены в пространстве внутренней памяти DSEG по адресам SOH, 90H, ОАОН, ОВОН и ничем не отличаются от обычных ячеек памяти. Отказ от изолированного пространства ВВ, используемого в архитектуре ВЕ48, позволил увеличить вычислительную эффективность МС интенсивного ВВ, привел к более регулярной структуре набора команд ВЕ51. Если ранее для увеличения возможностей арифметическо-логической обработки данных В В было необходимо вводить ряд новых команд:

ANL port,A ;port<-port AND A

ORL port,A

;port<-port OR A

то теперь любая команда с операндом из внутренней памяти может быть применена к содержимому портов РО-РЗ.

Кроме того, порты РО-РЗ совмещены с битовым пространством BSEG, что обеспечивает доступ к отдельным его разрядам независимо от других. Порты РО-РЗ занимают адреса BSEG: 80Н-87Н, 90Н-97Н, ОАОН-ОА7Н и ОВОН-ОВ7Н соответственно.

Расширение пространства В В может быть выполнено за счет области XSEG или другими средствами с помощью самих портов РО-РЗ и SBUF.

При обращении к внешней памяти программ или данных порты РО, Р2 выполняют функции системных шин AD и А В соответственно. Младший байт адреса и данные передаются через РО в мультиплексном режиме: сначала выводится адрес, а затем для передачи данных используется порт. Старший байт адреса формируется на Р2. Линии порта РЗ реализуют управление циклами обмена и другие специальные функции аппаратного уровня:

РЗ.О R x D Вход приемника последовательного канала

Р3.1 TxD Выход передатчика последовательного канала

P3.2 INTO Вход запроса на

прерывание О

РЗ.З INT1 Вход запроса на прерывание 1

Р3.4 ТО Внешний вход таймера/счетчика О

Р3.5

Т1

Внешний вход таймера/счетчика 1

Р3.6 wr . строб записи в XSEG

Р3.7 RD Строб чтения XSEG

В случае МК 8052 две линии Р1 также выполняют специальную функцию

Pl.O

T2

Внешний вход таймера/счетчика 2

Pl.l T2EX Вход управления автоматической перезагрузкой

таймера/счетчика 2

Порты РО-РЗ имеют организацию, во многом схожую с организацией портов ВЕ48 . Отличие состоит лишь в выходном буфере, который значительно модифицирован. Так, в портах РО и Р2 в выходном буфере предусмотрены ключи, соединяющие их выводы с внутренними шинами AD и А соответственно. Поэтому при обращении к внешним средствам содержимое выходного регистра порта Р2 не изменяется, а содержимое РО становится равным OFFH. Буферные каскады

порта РЗ построены так, что для выполнения специальной операции соответствующий разряд выходного регистра РЗ должен быть установлен в 1. Иначе на выходе будет 0.

Совмещение специальных функций с портом РЗ позволило расширить число портов ВВ с трех для ВЕ48 до четырех для ВЕ51 при тех же ограничениях на ширину физического интерфейса. Однако это усложнило выходной буфер РЗ.

Порты Р1-РЗ имеют встроенную нагрузку, тогда как для порта РО, выполненного по схеме с открытым коллектором, требуется внешняя нагрузка. Каждый вывод портов РО-РЗ может быть использован в качестве выходного независимо от других. Для перевода какого-либо вывода в режим входа в соответству-ющий разряд выходного регистра должна быть записана 1. При сбросе МК состояние всех портов устанавливается равным OFFH.

Следует отметить, что в отличие от ВЕ48 в МК ВЕ51 все 32 вывода портов РО-РЗ тестируются индивидуально с помощью условных команд ветвления:

JB bit,

rel

;Если

BSEG(bit)=l, то

;SJMP rel

JNB bit, rel

;Если

BSEG(bit)=0, то

;SJMP rel

JBC bit, rel

;Если

BSEG(bit)=l, to

;SJMP rel

;и BSEG(bit)<-0

Последняя команда после тестирования всегда на выводе порта, как и в любом другом разряде из пространства BSEG, устанавли-вает 0.

Последовательный канал связи. В состав ВЕ51/8052 входит дуплексный канал последовательной связи с буферизацией, ко-торый может быть запрограммирован для работы в одном из четырех режимов:

режим 0 - синхронный последовательный ВВ со скоростью OSC/12;

режим 1-асинхронный с 10-битовым кадром и переменной скоростью передачи;

режим 2-асинхронный с 11-битовым кадром и фиксированной скоростью передачи OSC/32 или OSC/64;

режим 3-асинхронный с 11-битовым кадром и переменной скоростью передачи.

Входные и выходные данные хранятся в буферном регистре SBUF с адресом 99Н. Управление работой приемопередатчиков осуществляется через слово управления и состояния SCON, расположенное в регистре по адресу 98Н:

SCON.О RI Флаг

прерывания приемника

SCON.l TI Флаг прерывания передатчика

SCON.2 RB8 Восьмой бит приемника в режимах 2 и 3. В режиме 1, если SM2=0. то отображает стоп-бит. В режиме 0 не используется

SCON.3 ТВ8 Восьмой бит передатчика в режимах 2 и 3

SCON.4 REN Разрешение приема

SCON. 5 SM2 Запрещение приема кадров с нулевым восьмым битом данных. В режиме 0 должен быть сброшен

SCON.6 SM1 Младший разряд для кодирования номера режима

SCON. 7 SMO Старший разряд для кодирования номера режима:

SM1 SM0 Режим SM1 SM0 Режим

0 0 0 1 0 2

0 1 1 1 1 3

Таймеры/счетчики. К стандартным средствам поддержки режима реального времени относятся таймеры/счетчики и подсис-тема прерываний. Если таймеры необходимы для организации системных меток реального времени и отработки временных интервалов, то подсистема прерываний обеспечивает своевремен-ную реакцию МК на асинхронные события, происходящие как внутри МС, так и вне ее.

В состав ВЕ51 входят два 16-разрядных таймера/счетчика СТО, СТ1. Еще один (СТ2) добавлен в архитектуре 8052. Состояние таймеров/счетчиков отражается программно-доступными регист-ровыми парами (ТНО, TLO), (TH1, TL1) и (ТН2, TL2) соответст-венно, размещенными в пространстве DSEG по адресам (8СН, 8АН), (8DH, 8ВН) и (OCDH, ОССН).

Таймеры/счетчики СТО-СТ2 могут быть запрограммированы для работы либо в качестве таймера, либо в качестве счетчика. Функция таймера состоит в счете числа машинных циклов, следующих с частотой OSC/12. Функция счетчика заключается в отслеживании числа переходов из 1 в 0 на соответствующих входах ТО, Tl, T2.

Управление режимом работы СТО, СТ1 осуществляет регистр TMOD (Timer/Counter Mode), который расположен по адресу 89Н. Регистр разбит на два 4-разрядных подрегистра TOMOD и T1MOD, которые ответственны за управление СТО и СТ1 соответственно:

TMOD.О МО Младший бит поля управления режимом СТО

TMOD.l Ml Старший бит поля управления режимом СТО:

МО М1 Режим МО Ml Режим

0 0 0 1 0 2

0 1 1 1 1 3

TMOD.2 C/TN Выбор функции таймера или счетчика СТО. При С/Т=0 выбирается функция таймера, в против-ном случае счетчика

TMOD.3 GATE Флажок управления работой СТО. При GATE=1 работа разрешается, если INTO=1 и TRO=1 (см. TCON). При GATE = 0 работа счетчика зави-сит только от состояния TRO

TMOD.4

МО

То же, но для СТ1

TMOD.5

Ml

To

же, но для СТ1

TMOD.6 С/Т То же, но

для СТ1

TMOD.7 GATE To же, но для СТ1

За управление СТО, СТ.1 также ответствен регистр TCON (Timer/Counter Control), расположенный по адресу 88Н:

TCON.O ITO Управление типом входа INTO. При ITO=1

программируется динамический по срезу тип входа, в противном случае-статический

TCON.l IEO Флажок запроса прерывания INTO при динами-ческом входе. При подтверждении прерывания сбрасывается

TCON.2 IT1 то же, что и ITO, но для INT1

TCON.3 IE1 то же, что и IEO, но для INT1

TCON.4 TRO Флажок программного запуска/останова СТО

TCON.5 TFO Флажок переполнения СТО, который вызывает запрос прерывания. При подтверждении прерыва-ния сбрасывается

TCON.6 TR1 То же, что и TRO, но для СТ1

TCON.7 TF1 То же, что и TFO, но для СТ1

Младшая половина регистра используется для управления входами запроса на прерывания INTO и INT1, старшая-для управления непосредственно СТО и СТ1.

Для управления работой СТ2 служит регистр T2CON (Timer/ Counter 2 Control), расположенный по адресу ОС8Н:

T2CON.O CP/RL2 Флажок захвата/автозагрузки СТ2. При

CP/RL2=1 захват текущего состояния СТ2 осу-ществляется по срезу Т2ЕХ, если EXEN2==1. При CP/RL2 = 0 разрешается автозагрузка СТ2, если он переполнен или по срезу Т2ЕХ, если EXEN2 = 1. Этот флажок не принимается во вни-мание при RCLK=1 или TCLK=1, т.е. когда СТ2 работает в качестве генератора скорости

T2CON. 1 С/Т2 Управление функцией таймера (С/Т2=0) или счетчика (С/Т2=1)

T2CON.2 TR2 Программный запуск СТ2 при TR2=1 и останов в противном случае

T2CON.3 EXEN2 Флажок разрешения динамическому по срезу вхо-ду Т2ЕХ осуществлять захват/автозагрузку СТ2, если он не работает в режиме генератора скорос-ти последовательного порта. Функция активи-руется при EXEN2=1

T2CON.4 TCLK При TCLK=1 CT2 используется

передатчиком последовательного канала, работающего в режи-ме 1 или 3, в качестве

генератора скорости пере-дачи. При TCLK=0 генератором

служит СТ1

T2CON.5 RCLK То же, что и TCLK, но

для приемника после-довательного канала

T2CON.6 EXF2 Флажок

выполнения захвата/автозагрузки, выз-ванного изменением состояния на Т2ЕХ при

EXEN2

= 1. При разрешенном прерывании вызы-вает запрос. Сбрасывается только

программным способом

T2CON.7 TF2 Флажок

переполнения CT2. Также вызывает запрос на прерывание. Функция установки

подав-ляется при TCLK=1 или RCLK=1

При захвате текущего состояния или при повторной авто-загрузке в управлении работой CT2 участвует также 16-разрядный регистр RCAP2 (Reload/Capture Timer/Counter 2), расположенный в двух соседних 8-разрядных ячейках с адресами ОСАН (RCAP2L) и ОСВН (RCAP2H).

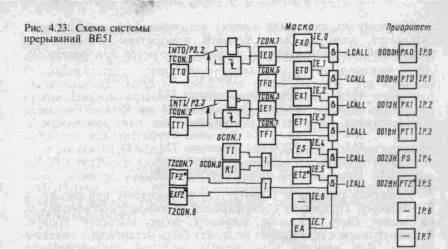

Система прерываний. Архитектура ВЕ51 поддерживает двух-уровневую приоритетную систему прерываний с пятью (или шестью в случае 8052) источниками запросов на обслуживание, имеющими фиксированные векторы прерываний. Программное управление системой осуществляется через два 8-разрядных регистра: IP (Interrupt Priority)-регистр приоритета прерываний и IE (Interrupt Enable)-регистр разрешения прерываний. Услов-ная схема системы прерываний представлена на рис. 4.23.

Для приема внешних запросов на прерывание служат линии INTO и INT1, которые могут быть запрограммированы на срабатывание как по переходу из одного состояния в другое, так и по уровню входного сигнала независимо друг от друга. Управле-ние типом входа осуществляется флажками ITO/TCON.O (Interrupt Type 0) и IT1/TCON.2. При ITi=l устанавливается режим срабатывания по переходу из 1 в 0, в противном случае-по напряжению низкого уровня на входе INTi, i=0-1. Запросы на

прерывание от внешних источников INTO или INT1 устанавливают флажки IEO/TCON.1 (Interrupt Edge 0) и IE1/TCON.3. В случае работы по переходу эти флажки сбрасываются автоматически при входе в соответствующую процедуру обслуживания прерывания. В случае режима работы по уровню флажки отслеживают

состояние сигналов на входных линиях INTO и INT1, повторяя все их изменения.

Источниками внутренних запросов могут быть: флажок TFO/TCON.5 (Timer Flag 0)-признак переполнения СТО, флажок TF1/TCON.7-признак переполнения СТ1, а также флажок TI/SCON.l (Transmit Interrupt) или флажок RI/SCON.O (Recive

Interrupt). Еще одним источником внутреннего прерывания в случае 8052 могут быть флажки TF2-признак переполнения СТ2 или EXF2, входящие в состав T2CON. Флажки внутренних запросов TFO и TF1 очищаются автоматически при переходе к соответствующей процедуре обслуживания, тогда как состояние флажков TI, RI, а также TF2, EXF2 не изменяется. Процедурой обслуживания прерываний эта информация используется для уточнения источника запроса по методу поллинга, а затем сбрасывается с помощью подходящей для этого команды.

Все флажки, которые фиксируют запросы на прерывания, могут быть установлены программным способом, что дает возможность реализовать вызов соответствующих процедур обслуживания непосредственно из программ. Этому способствует дублирование входов INTO и INT1 программно-управляемыми флажками IEO и IE1. Каждый из пяти (или шести) источников прерываний может быть замаскирован независимо от других с помощью регистра маски IE:

IE.O ЕХО Маска IEO или INTO

IE.1 ЕТО Маска TFO ___

IE.2 ЕХ1 маска IE1 или INT1

IE.3 ЕТ1 Маска TF1

IE.4-

ES

Маска TI+RI

IE.5 ЕТ2 Маска TF2 + EXF2

IE.6 - Не используется

IE.7 - ЕА Общее разрешение прерываний

Старший разряд регистра используется для блокировки или разрешения работы всей системы прерываний.

Каждому из пяти (или шести) источников прерываний присваивается один из двух уровней приоритета сбросом или установкой соответствующего разряда в регистре приоритета IP:

IP.O PXO Приоритет

IEO или INTO

IP.1 РТО Приоритет TFO ___

IP.2 РХ1 Приоритет IE1 или INT1

IP.3 РТ1

Приоритет TF1

IP.4 PS Приоритет TI + RI

IP.5 РТ2

Приоритет TF2+EXP2

IP.6 - Не используется

IP.7 - Не используется

Установка разряда в 1 соответствует высокому приоритету, в О-низкому. Процедура обслуживания низкоприоритетного уров-ня может быть прервана запросом более высокого уровня. Высокоуровневое прерывание не может быть остановлено никаким другим. Для решения конфликтных ситуаций одновременного появления нескольких запросов одного уровня используется схема вторичного арбитража, устанавливающая строгое отношение предпочтения между всеми источниками запросов:

Источник

Приоритет

IEO

0 (высший)

TFO

1

IE1

2

TF1

3

RI+TI

4

TF2+EXF2

5 (низший)

Запросы на прерывания могут быть приняты к обслуживанию в конце каждого командного цикла, за исключением исполнения RETI или команды с любым видом доступа к регистрам IE и IP. Данное исключение гарантирует выполнение хотя бы еще одной инструкции после команд обращения к IE или IP и RETI, прежде чем возникнет новое прерывание программы. При фиксации запроса аппаратура МК генерирует команду

LCALL vect

обеспечивая переход к стартовому адресу vect соответствующей процедуры обслуживания. С каждым источником связан свой стартовый адрес (вектор прерывания):

ЕХTI0

IEO

0003H

TIMERO

TFO

OOOBH

EXTI1

ТЕ1

001 ЗН

TIMER1

TF1

001 ВН

SINT

RI+TI

0023H

TIMER2

TF2+EXF2

002ВН

В некоторых случаях эта команда одновременно с переходом к стартовому адресу сбрасывает флажок, вызвавший данное преры-вание. При переходе к процедуре обслуживания текущее состояние PC загружается в стек, обеспечивая возврат по команде RETI, заканчивающей каждую процедуру обслуживания. Эта команда отличается от обычной инструкции возврата RET тем, что сообщает системе прерываний об окончании текущей процедуры обслуживания, что необходимо для управления двухуровневой системой приоритетов.

В состав ВЕ51 входит еще один общецелевой регистр управления PCON (Power Control), расположенный по адресу 87Н. Состав этого регистра зависит от технологии изготовления МК. При п-МОП-технологии PCON содержит всего лишь один флажок SMOD. Полный состав флажков можно встретить только в КМОП-вариантах:

PCON.O IDL Установка бита активизирует режим свободного состояния

PCON.l PD Установка бита активизирует режим пониженной мощности

PCON.2 GFO Общецелевой флажок

PCON.3 GF1 Общецелевой флажок

PCON.4 - Не используется

PCON. 5 - Не используется

PCON.6 - Не используется

PCON.7 SMOD Активизирует двойную скорость приема/передачи последовательного канала, работающего в режи-мах 1, 2 и 3

Все управляющие регистры кроме PCON совмещены с прост-ранством BSEG, что обеспечивает доступ к отдельным их разрядам с помощью команд булевой группы. При сбросе МК управляющие регистры принимают нулевые значения за исключе-нием следующих:

IP (ВЕ51) ХХХОООООВ SBUF

ХХХХХХХХВ

IP(BE52)

XXOOOOOOB

PCON(n-MOn) OXXXXXXXB

IE(BE51)

OXXOOOOB

PCON(KMOn) OXXXOOOOB

IE(BE52)

OXOOOOOOB

4.12. Система команд ВЕ51

Система насчитывает 111 команд, из них 49 однобайтовых, 45 двухбайтовых и 17 трехбайтовых. Появление трехбайтовых команд связано с расширением объемов CSEG и XSEG, а также вводом прямой адресации в DSEG. Все команды выполняются за один или два машинных цикла (12 тактов ALE) за исключением команд MUL и DIV, которые требуют четыре цикла. Большинст-

во двухбайтовых команд одноцикловые, а все трехбайтовые команды-двухцикловые. Это объясняется тем, что за один машинный цикл в ВЕ51 может вводиться до двух байтов программного кода.

Все множество команд ВЕ51 удобно разбить на пять групп:

пересылки (28), логической обработки (25), арифметической обра-ботки (24), передачи управления (17), булевого процессора (17).

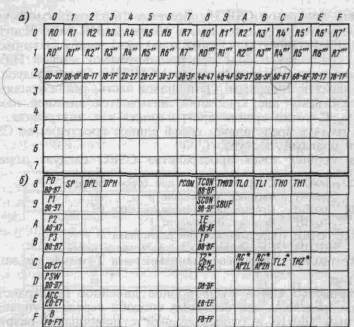

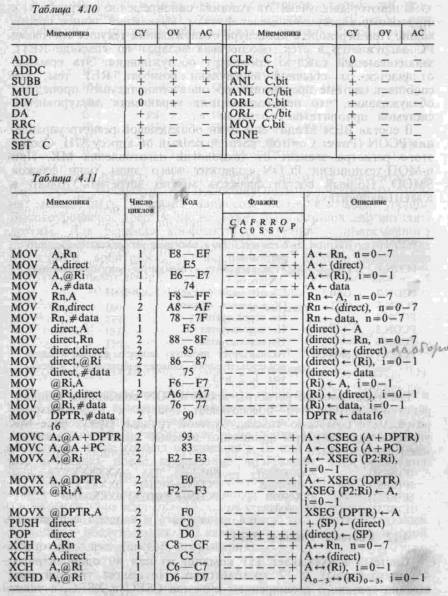

В процессе исполнения команды влияют на ряд флажков-признаков результата, входящих в состав PSW (табл. 4.10). Признак Р устанавливается всякий раз, когда приемником результата служит аккумулятор, включая операции пересылки.

Группа команд пересылки (табл. 4.11) содержит команды MOV (пересылки данных между DSEG и RSEG), MOVC (между CSEG и A), MOVX (между XSEG и А или RSEG), команды обращения к стеку PUSH и POP, а также две команды обмена ХСН и XCHD. Наиболее емкой инструкцией является команда MOV, которая использует четыре способа адресации: регистровый (A, Rn, DPTR), прямой (direct), косвенный (@Ri) и непосредственный (#data, #data 16). Для указания приемника служат три способа адресации (кроме непосредственного), для указания источника все четыре. Трехбайтовая команда MOV direct, direct обеспечивает пересылку между двумя любыми ячейками памяти, включая регистры МК. Тем не менее для обмена с регистрами предусмотрены специальные двух- и однобайтовый форматы:

MOV Rn,direct

MOV direct,Rn

MOV A,Rn

MOV Rn,A

Их использование позволяет существенно сократить длину про-граммного кода. Специальная команда

MOV DPTR,#datal6

позволяет загрузить 16-разрядный указатель DPTR значением data 16.

При выполнении команды MOVC считывания данных из программной памяти могут быть применены два способа адреса-ции: по базе DPTR и относительный. В обоих случаях целое без знака смещение (индекс) хранится в аккумуляторе. Приемником результата также служит аккумулятор. Команда дает возможность выполнять быструю перекодировку по таблицам, осуществлять доступ к массивам памяти.

Обращение к внешней памяти осуществляется с помощью команды MOVX. Обмен производится по байтам между аккумуля-тором и ячейкой внешней памяти данных. Ячейка XSEG может бьпь адресована двумя способами: косвенно через 16-разрядный указатель DPTR п страничпо косвенно через 8-разрядный указа-тель Ri, i=0-l. В последнем случае регистром страниц служит выходной регистр Р2.

Операции PUSH и POP используют только прямой способ адресации, однако это не мешает им манипулировать содержимым регистров, которые рассматриваются как ячейки памяти.

Две типовые операции обмена ХСН и XCHD дополняют одностороннюю пересылку двусторонней. При выполнении опера-ции ХСН обмену подлежат байты, при XCHD-младшие тетрады байтовых операндов.

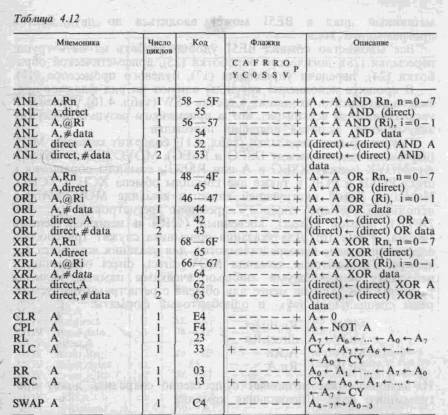

Приведенная в табл. 4.12 группа команд логических операций содержит три типовые двухместные операции: ANL-логическое И, ORL-логическое ИЛИ и XRL-логическое исключающее ИЛИ. Источником первого операнда и одновременно приемником результата служит либо аккумулятор А, либо прямо адресуемая ячейка памяти. Второй операнд задается одним из четырех основных методов адресации. В состав группы входит также ряд одноместных операций: CLR-очистки, CPL-логического дополнения (инверсия), а также RL, RLC, RR и RRC-операции

циклического и расширенного сдвигов вправо и влево. Все операции манипулируют содержимым только аккумулятора А. Сюда же включена операция обмена тетрад в аккумуляторе SWAP, которая может интерпретироваться как циклический сдвиг байта на четыре разряда.

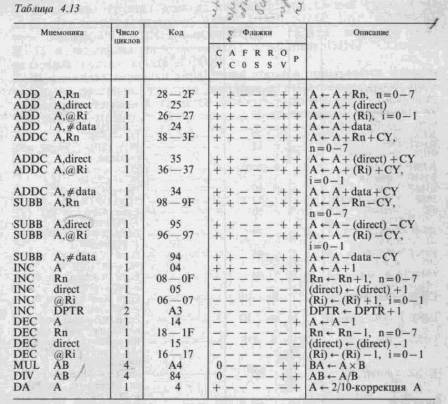

В состав группы команд арифметической обработки (табл. 4.13) входят: операция сложения ADD, сложения с учетом переноса ADDC, вычитания с учетом займа SUBB, увеличения и уменьше-ния на единицу INC и DEC, десятичная коррекция сложения в 2/10-коде упакованного формата DA, умножение MUL и деление DIV. Операции выполняются над беззнаковыми целыми числами.

В операциях сложения и вычитания первым операндом и приемником результата служит аккумулятор. В качестве второго операнда выступает либо рабочий регистр Rn, n=0-7, выбран-ного регистрового банка, либо ячейка памяти данных, адресуемая прямо direct или косвенно @Ri, i=0-l, либо непосредственные данные #data. Операции INC и DEC применимы к аккумулятору,

одному из рабочих регистров или к ячейке памяти, адресуемой как прямо, так и косвенно. Кроме этого операция увеличения на единицу может быть применена к содержимому регистра указате-ля DPTR.

В операциях целочисленного умножения и деления без зна-ка участвуют аккумулятор и регистр В. При умножении 8-раз-рядное значение А умножается на 8-разрядное значение В, а 16-разрядный результат записывается в пару ВА. При этом регистр В хранит старшую часть произведения. Флажок пере-полнения OV устанавливается, если произведение больше 255. При делении 8-разрядного значения А на 8-разрядное значение В частное записывается в А, а остаток в В. При попытке деления на О устанавливается флажок переполнения. Операция десятичной коррекции для сложения DA осуществляется стандартным способом

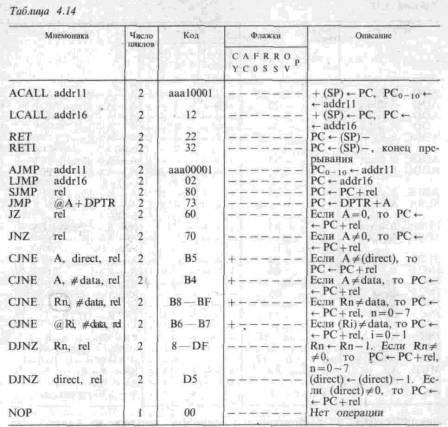

В составе группы команд передачи управления (табл. 4.14) находятся команды перехода AJMP, LJMP, SJMP, JMP, условного перехода JZ, JNZ, CJNE, вызова ACALL, LCALL, возврата RET, RETI и модификации с условным переходом DJNZ. Сюда же включена пустая команда NOP.

В командах передачи управления широко применяется относительная адресация, которая поддерживает перемещаемые программные модули. В качестве относительного адреса выступает 8-разрядное смещение rel со знаком, обеспечивающее ветвление от текущего положения PC в обе стороны на +127 байт. Для перехода в любую другую точку 64К-байтового адресного пространства может быть использован либо прямой addrl6, либо косвенный @A+DPTR адрес. В последнем случае содержимое А интерпретируется как целое без знака. Вариант короткой прямой адресации addrll внутри 2К-байтовой текущей страницы введен для совместимости с архитектурой ВЕ48.

Все эти типы адресации могут быть применены только к операции перехода, а для операции вызова допустимы только прямой addrl6 и внутристраничный addrll способы адресации. Во всех условных операциях может использоваться только относи-тельная адресация.

Когда МК ВЕ51 опознает запрос на прерывание, она генери-рует одну из команд типа LCALL addrl6, что автоматически обеспечивает запоминание адреса возврата в стеке. Однако в отличие от ВЕ48 в ВЕ51 нет автоматически сохраняемой информации о состоянии. При этом логика прерываний перестает срабатывать на запросы того уровня, который был принят к обслуживанию. Для понижения уровня прерывания служит команда возврата из прерывания RETI, которая кроме операции, эквивалентной RET, включает операцию разрешения прерывания данного уровня.

К типовым условным операциям ВЕ51 относятся также операции JZ и JNZ, JC и JNC. Две последние включены в группу булевых. Однако появилась новая операция <Сравнить и перейти> CJNE. По данной команде операнд сначала сравнивается по правилам вычитания целых чисел с константой и в соответствии с результатом сравнения выставляется флажок CY. Затем в случае несовпадения с константой выполняется ветвление. Сравнивая аккумулятор, регистр или ячейку памяти с последовательностью констант, получаем удобный способ проверки на совпадения, например с целью выявления особых случаев. По сути дела команда CJNE является элементом оператора языков высокого уровня типа CASE.

Дальнейшее развитие получила и команда DJNZ. Теперь программист в качестве счетчика может использовать не только один из рабочих регистров Rn, n==0-7, но и любую ячейку памяти данных DSEG.

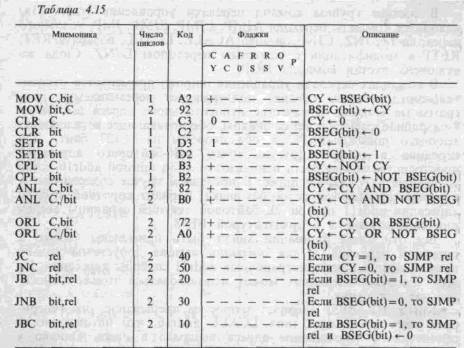

Ряд команд, предназначенных для выполнения операций пересылки, проверки условий и логической обработки булевых (одноразрядных) переменных, образует отдельную группу (табл. 4.15). В качестве одного из операндов они применяют флажок переноса CY, в качестве другого служит прямо адресуемый элемент пространства BSEG. Флажок CY при выполнении операций И и ИЛИ может рассматриваться как булевый аккумулятор.

В группу входят также операции безусловного и условного переходов с относительным 8-разрядным смещением rel. Условный переход может быть осуществлен как при установленном JB, так и при сброшенном JNB бите. Наличие команд с прямым адресом проверяемого бита объясняет отсутствие специальных команд проверки тестовых входов, которые были в ВЕ48. Особо следует отметить операцию JBC, которая реализует ветвление при установленном бите и одновременно с этим сбрасывает его в 0. Такая операция полезна в системах, решающих много задач, при организации семафоров, которые вводятся для защиты коллективно используемых ресурсов МС.

Семафор представляет собой расположенный в памяти флажок, информирующий о состоянии связанного с ним ресурса: 1-<Свободно>; 0-<Занято>. Захват ресурса допускается только в случае,

если он свободен, затем семафор должен быть переведен в состояние <Занято>. Захват ресурса с помощью команды JBC осуществляется следующим образом:

WAIT: JBC bit.OK ;Проверка семафора bit

SJMP WAIT ;Pecypc занят, ожидание

OK: - ;Ресурс захвачен

4.13. Функциональное описание ВЕ51

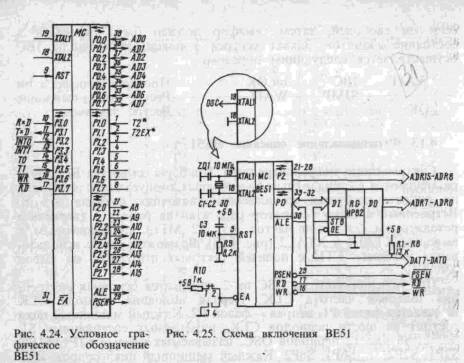

Синхронизация микроконтроллера. Приборы семейства ВЕ51/8052 размещаются в стандартных 40-выводных корпусах (рис. 4.24), для их работы требуется единственный источник питания +5 В. Встроенный в схему генератор рассчитан на работу с кварцевым резонатором (диапазон частот 3,5-12 МГц), подключенным к выводам XTAL1 и XTAL2 (рис. 4.25). Возможно также использо-вание внешнего ГТИ с подачей тактовых импульсов на вывод XTAL1.

При делении частоты OSC на 2 получается основная внутренняя тактовая частота CLK. Первая половина периода CLK называется фазой Р1, вторая-фазой Р2. Каждый машинный цикл состоит из шести -периодов CLK, называемых состояниями S1, S2, ..., S6 или 12 периодов OSC, называемых фазами S1P1, S1P2, S2P1, S2P2, ..., S6P1, S6P2. Каждый машинный цикл сопровожда-ется генерацией двух стробов ALE длительностью в один период CLK, которые размещаются в фазах S1P2-S2P1 и S4P2-S5P1 соответственно. Период следования ALE (машинный полуцикл) равен 6 периодам OSC.

Командный цикл МК содержит несколько машинных циклов и отсчитывается от фазы S1P1. По фазе S1P2 в IR фиксируется код операции. Второй байт двухбайтовой команды читается в S4P2 того же машинного цикла, третий-в S1P2 следующего. Таким образом, для ввода каждого байта требуется один машинный полуцикл. Во время всех оставшихся полуциклов в фазах S1P2 и S4P2 читается код операции следующей размещенной в памяти команды. Однако байт в IR не вводится и PC не инкрементируется, что приводит к его игнорированию. Ввод повторяется до окончания текущего командного цикла, который всегда завершает-ся в фазе S6P2. Вслед за этим начинается новый командный цикл с вводом в IR кода операции следующей по исполнению команды.

Другую временную последовательность исполнения имеет однобайтовая двухцикловая команда обращения к внешнему ОЗУ данных MOVX. Доступ к ОЗУ реализуется во втором машинном цикле, поэтому первый машинный цикл соответствует общей схеме, а во втором отсутствуют пустые операции FETCH. Во время второго машинного цикла первый строб ALE отсутствует, так как доступ к внешнему ОЗУ требует всего машинного цикла.

Запись результата операции в порты РО-РЗ реализуется в фазе S6P2 последнего машинного цикла соответствующей коман-ды, однако на выходе порта новое значение появляется только в следующей фазе S1P1. При записи в порты Р1-РЗ информации, требующей перехода из 0 в 1, через выходную цепь в течение S1P1 и S1P2 пропускается импульс тока, амплитуда которого в 100 раз превышает номинальное значение. Это делается для повышения скорости переключения выходных сигналов. Порт РО такими свойствами не обладает.

Выходы портов Р1-РЗ обеспечивают управление четырьмя маломощными ТТЛ-входами (1оь=1,6 мА). Нагрузочная способ-ность порта РО IoL=3,2 мА. Однако для его работы требуются внешние нагрузочные резисторы, за исключением случая работы в режиме AD.

Считывание данных, присутствующих на входе портов РО, Р1, выполняется по фазе S5P1 последнего машинного цикла команды, а на входе портов Р2, РЗ-по фазе S5P2.

Вход RST служит для приведения МК в исходное состояние. Сигнал запроса воспринимается всякий раз, когда на входе RST удерживается напряжение высокого уровня более двух машинных циклов (24 периода OSC) при условии, что генератор запущен. В течение следующего машинного цикла формируется внутренний сигнал сброса, который повторяется до тех пор, пока вход RST активен. При внутреннем сбросе установка регистров МК осуществляется следующим образом:

PC

OOOOH

T2CON(BЕ52) ООН

АСС ООН ТНО ООН

В ООН TLO ООН

PSW ООН ТН1 ООН

SP

07H

TL1

ООН

DPTR

OOOOH

TH2

ООН

РО-РЗ

OFFH

TL2

ООН

1Р(ВЕ51) ' ХХХОООООВ

РСАР2H(ВЕ52) ООН

IP(BE52)

XXOOOOOOB

РСАР2H(ВЕ52) ООН

IE(BE51)

OXXOOOOOB

SCON

ООН

IE(BE52)

OXOOOOOOB

SBUF

ХХН

TMOD

ООН

РСОМ(п-МОП) ОХХХХХХХВ

TCON

ООН

PCON(KMOn)

ОХХХООООВ

Схема автоматического сброса МК при включении источника питания приведена на рис. 4.25. Указанные на схеме элементы RC-цепочки обеспечивают длительность импульса RST, достаточную для стабилизации генератора и последующего за ней сброса МК.

Микроконтроллеры семейства ВЕ51 осуществляют режим хранения записанных в их внутреннюю память данных при выключенном источнике питания +5 В. В данном режиме запасное напряжение питания поступает на вход RST, а ток потребления очень мал. При подаче напряжения +5 В запасной источник должен оставаться во включенном состоянии еще два машинных цикла, в течение которых выполняется общий сброс МК.

В КМОП-вариантах для перехода в режим с малым потребле-нием используются флажки PD и IDL в PCON. При установке флажка IDL работа генератора не прекращается и, следовательно, все внутренние ПУ продолжают работать. При установке флажка PD работа генератора прекращается. Выход из состояния IDL = 1 может быть осуществлен по прерыванию или с помощью общего сброса. Выход из режима останова с пониженной мощностью (PD=1) может произойти только с помощью общего сброса.

В МК не предусмотрен вход пошаговой отладки, как это сделано в ВЕ48. С этой особенностью ВЕ51 связано усложнение отладочных средств для МС на его основе. Приходится либо разрабатывать специальные диагностические кристаллы, например 8051Е, либо проектировать сложные аппаратные средства, под-ставляющие в <прозрачном> для пользователя режиме специаль-ные циклические программы. Однако существует еще одна возможность организации пошагового режима работы, которая может быть использована в простейших системах отладки. Для этого резервируется один из входов INTO или INT1, который

программируется для работы в режиме статического входа. Простая программа обеспечивает тестирование, например входа INTO, с последующим выходом из прерывания;

JNB Р3.2,$ ;ждать пока TNTO=0

JB Р3.2,$ ;Ждать пока INTO= 1

RETI ;Возврат и выполнение одной команды

После генерации на входе INТО одного импульса (срез на входе INTO) выполняется команда RETI. Так как следующий запрос на прерывание может быть воспринят только при выполнении одной команды после RETI, гарантируется исполнение очередной инст-рукции из программы пользователя.

Интерфейс расширения. Как и в ВЕ48, внутренние ресурсы ВЕ51/8052 могут быть расширены внешними средствами. При этом память программ CSEG достигает 64К байт, а память данных увеличивается за счет ввода в действие внешней памяти XSEG, максимальная емкость которой тоже 64К байт. Внешняя часть CSEG и область XSEG могут быть объединены в одно физическое пространство. Расширение области ВВ выполняется за счет части пространства XSEG (совмещенный В В).

Для связи со средствами расширения МК имеет встроенную системную магистраль, которая физически частично совмещена с портами РО, Р1 и РЗ. В состав магистрали входят двунаправленная шина AD (порт РО), шина старшей части адреса А (порт Р2), стробы фиксации адреса ALE, чтения памяти программ PSEN, записи WP (линия Р3.6) и чтения RD (линия Р3.7) внешней памяти данных XSEG.

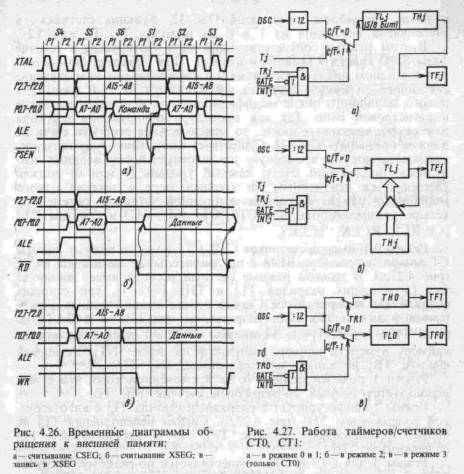

По срезу ALE передаваемая через порт РО младшая часть адреса фиксируется во внешнем регистре (см. рис. 4.25). Старшая часть принимается из порта Р2. Стробы PSEN (iql = 3,2 мА), RD и WR определяют тип доступа. При чтении CSEG (операция PSEN) данные считываются по фронту строба PSEN (фаза S1P1 и S4P1) (рис. 4.26, а), при чтении XSEG (операция RD)-по фазе S3P1

(рис. 4.26, б), при записи в XSEG (операция WR) данные действительны на всем стробе (рис. 4.26, в).

Цикл внешнего обращения к CSEG инициируется всякий раз при выходе адреса за пределы внутреннего ПЗУ, а также при ЕХ=0. Возможность отключения внутреннего ПЗУ используется в системах эмуляции МК и отладки МС на его основе. Цикл обращения к внешней памяти инициируется по команде MOVX.

В операциях обращения к внешней памяти участвуют порты РО (совмещенная магистраль AD), P2 (магистраль старшего адреса), а

также линии Р3.6 (строб WR) и Р3.7 (строб RD) порта РЗ. При работе порта РО в качестве линии AD содержимое связанного с ним выходного регистра теряется и принимает значение OFFH. Содержимое выходного регистра порта Р2 при работе в режиме адресной шины сохраняется и поступает на выводы порта в тех машинных циклах и полуциклах, когда нет обращения к внешней памяти.

Физическое совмещение пространств CSEG и XSEG выполняет-ся объединением стробов PSEN и RD в один строб чтения.

Работа таймеров/счетчиков. Каждый из таймеров/счетчиков СТО-СТ1 (СТ2) выполняет функцию таймера (С/Т=0) или счетчика (С/Т=1). Функция таймера состоит в счете синхроимпульсов, следующих с частотой OSC/12, функция счетчика-в счете числа переходов из 1 в 0 на выходах ТО, Т1 или Т2.

В этом режиме соответствующий вход тестируется в течение фазы S5P2 каждого машинного цикла. При обнаружении состоя-ния 1 в одном цикле и состояния 0 в следующем за ним значение связанного со входом счетчика увеличивается на 1. В фазе S3P1 нового машинного цикла модифицированное значение отражается в регистровой паре. Так как процедура обнаружения перехода длится два машинных цикла, то максимальная скорость счета не должна превышать OSC/24. Существует единственное ограничение, накладываемое на временную последовательность входных им-пульсов, подлежащих счету: каждый уровень (1 или 0) должен удерживаться неизменным по крайней мере в течение одного машинного цикла. В рамках выбранной функции определены четыре режима работы для СТО, СТ1 (МО, Ml) и три для СТ2 (CP/RL2, RCLK, TCLK).

Режим 0 таймеров/счетчиков СТО, СТ1 подобен режиму работы СТ микроконтроллера ВЕ48 с предварительным делителем на 32 (рис. 4.27,а). В данном режиме счетный регистр имеет длину 13 бит (5 младших разрядов TLj и THj, j==0-l), три старших разряда TLj игнорируются. Сигнал переполнения счетчика фикси-руется флажком TFj. Счет разрешается при TRj=l и GATE = О либо TRj=l и INTj = 1. Установка GATE=1 дает возможность

таймеру измерять ширину импульсов на входе INTj. Установка флажка TRj не влияет на содержимое THj, TLj.

Режим 1 подобен режиму 0, за исключением того, что в нем используется полный 16-разрядный счетчик ТН, TL.

Режим 2 конфигурирует 8-разрядный счетчик TLj с автозагруз-кой содержимым THj (рис. 4.27,6). Сигнал переполнения TLj не только устанавливает флажок TFj, но и перезагружает TLj содержимым THj.

Режим 3 для СТО и СТ1 осуществляется по-разному. В случае СТО два счетных регистра TLO и ТНО рассматриваются независи-мо друг от друга (рис. 4.27,в). Логика управления работой TLO аналогична режиму 1. Второй счетчик работает в режиме таймера, управляемого флажком TR1. Сигнал переполнения фиксируется флажком TF1. В случае СТ1 режим 3 останавливает счет, подобно тому, как это было при TR1 =0 в других режимах. Использование режима 3 позволяет увеличить число счетчиков МК ВЕ51 до трех, что может быть необходимо в некоторых практических случаях.

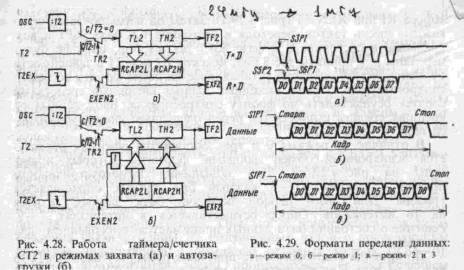

В МК 8052 имеется еще один 16-разрядный счетчик СТ2, который может работать в одном из трех основных режимов:

захвата (CP/PL2=1), автозагрузки (CP/RL2 =0) и генератора скорости (RCLK=1 или TCLK=1). В зависимости от состояния флага EXEN2 определены два варианта организации режима захвата (рис. 4.28,а). При EXEN2 = 0 сигнал переполнения СТ2

устанавливает флажок переполнения TF2. Дополнительно к этому при EXEN2=1 каждый переход из 1 в 0 на входе Т2ЕХ вызывает перезагрузку 16-разрядного регистра СТ2 значением, хранящимся в САР2, и установку флажка EXF2.

В режиме автозагрузки (рис. 4.28,6) каждое переполнение СТ2 кроме установки флага TF2 вызывает перезагрузку СТ2 значением из САР2. Одновременно с этим при EXEN2=1 реализуется возможность перезагрузки СТ2 переходом из 1 в 0 на входе Т2ЕХ и установку флажка EXF2.

При RCLK=1 или TCLK==1 устройство работает в режиме генератора скорости приемника или передатчика последовательно-го канала связи.

Работа последовательного канала связи. Встроенный в ВЕ51 последовательный канал связи может быть запрограммирован для работы в одном из четырех режимов. В режиме 0 (рис. 4.29,а) данные принимаются или передаются последовательно через линию RxD со скоростью OSC/12 младшими битами вперед по 8 разрядов за операцию. Для синхронизации внешних средств используется линия Т х D. Передача инициируется всякий раз, когда новые данные записываются в SBUF. Признаком окончания передачи служит установка флажка TI. Операция ввода данных активизируется при разрешенном приеме (REN=1) по сбросу флажка RI. Установка флажка RI свидетельствует о готовности введенных данных для считывания из SBUF.

Выдаваемый на линию Т х D синхросигнал переходит в состояние 0 в фазе S3P1 второго машинного цикла, следующего за циклом исполнения команды записи данных в SBUF или команды

сброса RI при REN=1 (рис. 4.29,а). Затем он переключается через каждые шесть тактов, переходя в состояние 1 в фазе S6P1 и воз-вращаясь в состояние 0 в фазе S3P1 до тех пор, пока не будут переданы или приняты все 8 бит. Флажок RI или TI в зависимости от выполняемой операции устанавливается после фронта восьмого синхроимпульса. Прием выходных данных внешними средствами следует осуществлять по фронту синхросигнала. Ввод данных от внешних средств выполняется перед очередным фронтом синхро-сигнала в фазе S5P2.

В отличие от режима 0 в трех оставшихся режимах реализуется асинхронный обмен данными, форматы которых приведены на рис. 4.29,б,в. Для повышения помехоустойчивости приема в режимах 1-3 каждый бит данных опрашивается трижды. Для этого период передачи бита данных делится на 16 интервалов. Опрос осуществляется в интервалах 7-9. Решение о состоянии бита данных принимается голосованием <два из трех>.

До прихода стартового бита приемник проверяет вход R x D 16 раз за период. При обнаружении перехода из 1 в 0 на входе R х D приемник начинает счет периодов передачи данных. В интервалах 7-9 первого периода приемник проверяет правильность генера-ции стартового бита. Если стартовый бит не подтверждается, то переход принимается за помеху, в противном случае реализуется операция последовательного приема 8 или 9 бит данных, которые запоминаются в регистре SBUF и во флажке RB8 (режим 2 и 3) при приеме последующего стопового бита. Одновременно с этим устанавливается флажок готовности приемника RI, свидетельствующий о приеме очередного кадра.

Данные передаются на вход Т х D после их записи в SBUF независимо от состояния TI. Передача стартового бита начинается в фазе S1P1 машинного цикла, следующего за первым сигналом переполнения счетчика, который используется в качестве генерато-ра скорости. Таким образом, начало передачи данных оказывается синхронизированным по отношению к генератору скорости. Кадр завершается выдачей стопового бита. Перед началом передачи стопового бита устанавливается флажок TI, свидетельствующий об окончании передачи данных.

В режимах 1-3 кадр данных имеет форматы, представленные на рис. 4.29,б,в. Если данные DO-D7 доступны через SBUF, то разряд D8-через флажки ТВ8 и RB8 управляющего слова SCON. В режиме 2 скорость передачи в зависимости от значения флажка SMOD в регистре PCON может быть равной либо OSC/32 (SMOD=0), либо OSC/64 (SMOD=1). В режиме 1 и 3 скорость передачи определяется частотой переполнения СТ1 или СТ2 (RCLK=1 или TCLK=1). В случае SMOD=1 скорость передачи совпадает с частотой переполнения, а при SMOD = 0 скорость передачи в 2 раза меньше. Таким образом, манипулируя флажком SMOD, можно понизить скорость передачи в режимах 1-3 в 2 раза.

Флажки RI и TI способны осуществлять запрос на прерывание. В режимах 1-3 установка флажка SM2 разрешает установку флажка RI и генерацию запросов от него только при приеме кадра с D8 = 1. Для режима 1 это соответствует контролю кадра на столовый бит. Для режима 2 и 3 такая организация работы обеспечивает разделение кадров на два класса в зависимости от состояния RB8. В противном случае принятые данные в SBUF не записываются и безвозвратно теряются.

Возможность реагировать только на кадры с RB8 = 1 учитывается при построении межмашинной магистральной сети, когда несколько подчиненных процессоров связаны через единую последовательную магистраль с главным процессором. Кадры с RB8 = 1 широковещательные, так как всегда воспринимаются всеми подчиненными процессорами. Они могут применяться для установления связи с одним из подчиненных узлов с последующим обменом информацией с помощью обычных кадров (RB8=0), которые игнорируются всеми процессорами, за исключением адресованного. Для вызова следующего процессора используется новый широковещательный кадр с новым адресом.